|

VHDL nbit - 8 bit parallel load shift - serial to parallel shift register structural design code test in circuit ISE Xilinx.

8 Bit Parallel In Serial Out Shift Register Vhdl Code Series Which FinalThis video is part of a series which final design is a Controlled Datapath using a structural approach.A Structural approach consist in designing all components needed for the design such as gates to form subsystems and then joining them together to form a larger design like adders and Arithmetic logic units,etc.First Shift Register This example creates a shift register using a VHDL signal called shiftreg shown in the code listing below.

8 Bit Parallel In Serial Out Shift Register Vhdl Code Serial To ParallelI am trying to take an 18 bit parallel load and change it into 9 two bit outputs using a shift register in vhdl. I have come up with the following code but am unsure of if I am thinking about this correctly. Architecture rtl of x is signal twoshifter: stdlogicvector(1 downto 0); signal loaddata: stdlogic; signal shiftenable: stdlogic; begin -Parallel to Serial shifter- shifter: process(clk, reset) begin if (reset 1) then twoshifter.

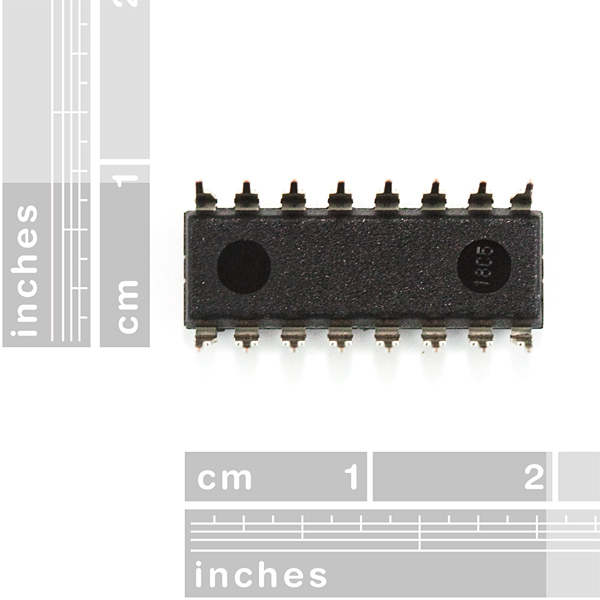

You need a place to hold all 9 bits simultaneously when you load them in parallel, and then a 1-bit output for you to shift each bit out in series. A 2-bit register can only hold 2 bits at once - you have nowhere to store the rest of the 18 bits you want to load in parallel. Also, again, your inputreg process needs to be rethought - do you really want a serial-load function as well. A shift register is written in VHDL and implemented on a Xilinx CPLD. Two different ways to code a shift register in VHDL are shown. Shift Register Operation A register stores data i.e. Logic levels, zeros and ones. A shift register has the capability of shifting the data stored in the register from left to right or right to left. Shift registers consist of D flip-flops as shown in the figure below. This is a four bit shift register and therefore consists of four D flip-flops. This shift register is configured to shift data from the left to the right. Data is fed into the D input of the first flip-flop on the left. Download game ppsspp dynasty warrior 6 iso ukuran kecilThis data can be either a 0 or a 1 and will be shifted to the right on each rising edge of the clock pulse. Whatever the state of the data input when the rising edge of the clock pulse occurs will be the logic level that is shifted into the first flip-flop. The data in each flip-flop will be shifted to the flip-flop on its right when the rising edge of the clock pulse occurs. A Shift Register is Made from D-type Flip-flops The image below shows an eight bit shift register that is created in VHDL code in this tutorial. Data is shifted from left to right from Most Significant Bit (MSB) to Least Significant Bit (LSB). The Shift Register as Created in VHDL Code It is also possible to shift data from right to left and to use the LSB as an input for serial data. Shift Register VHDL Code There are two examples of a shift register written in VHDL below. Bio rad cfx manager 31The two different examples create the same shift register using slightly different VHDL code. Both VHDL code examples of the shift register behave in exactly the same way when implemented on the CPLD.

0 Comments

Leave a Reply. |

AuthorTyra ArchivesCategories |

RSS Feed

RSS Feed